求:用与非门设计一个将8421BCD码转换为余3BCD码的组合逻辑电路_百度...看到你这么爱学习,还是告诉你好了 设A.B.C三台机器工作为1,不工作为0;机床正常工作为1,不正常为0 下面是满足题意的真值表 A B C Y 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 0 只允许也必须两台工作,不允许B和C同时工作 Y=ABC’+ACB’要用与非门表示,只能化成与非-与非形式...

怎么用74148优先编码器和与非门制作一个十线四线8421bcd码需要单独设计电路,以确保在特定输入组合下,正确产生所需的8421bcd码。总结而言,通过比较和分析十线-四线编码器与74148优先编码器的真值表,结合与非门的逻辑运算特性,可以设计出实现将十线信号编码为8421bcd码的电路。这一过程既需要对编码器原理的深入理解,也需要对逻辑电路设计的基本功。

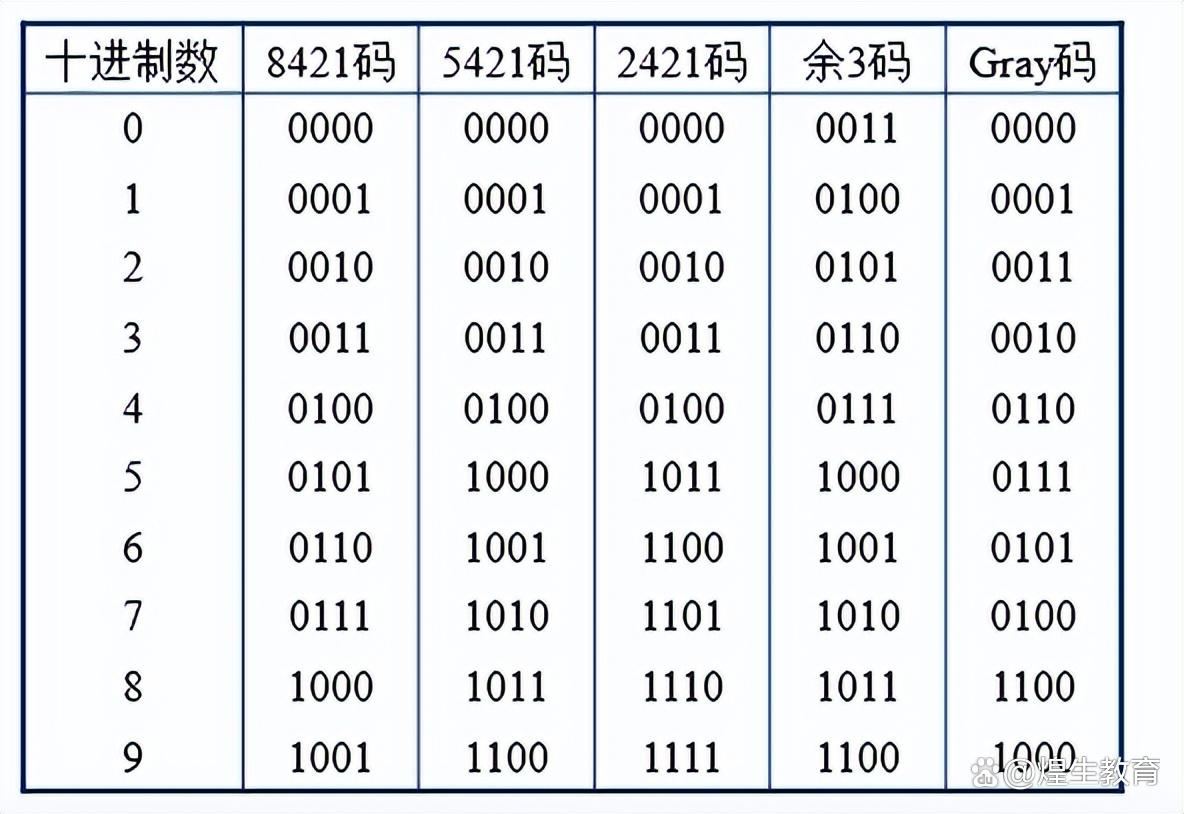

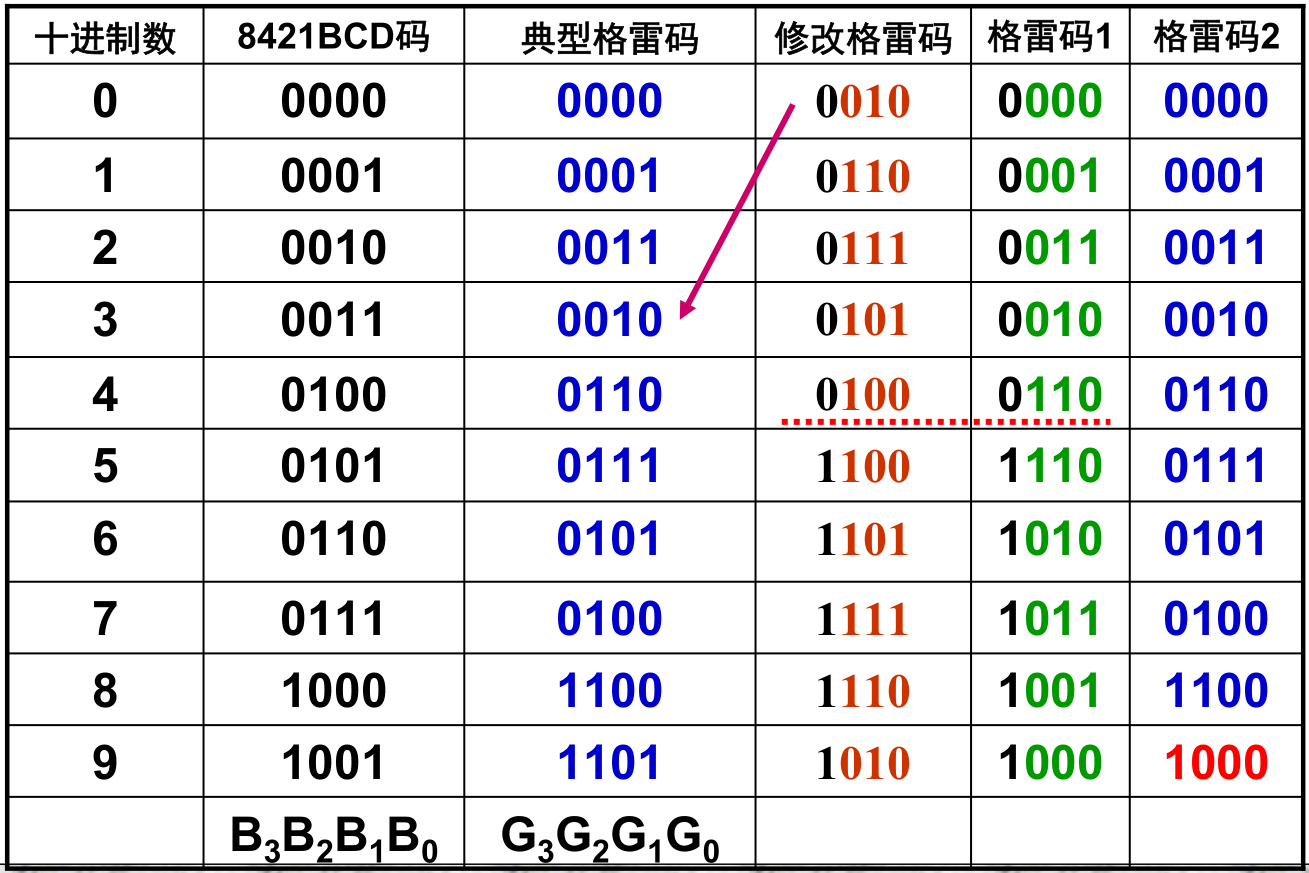

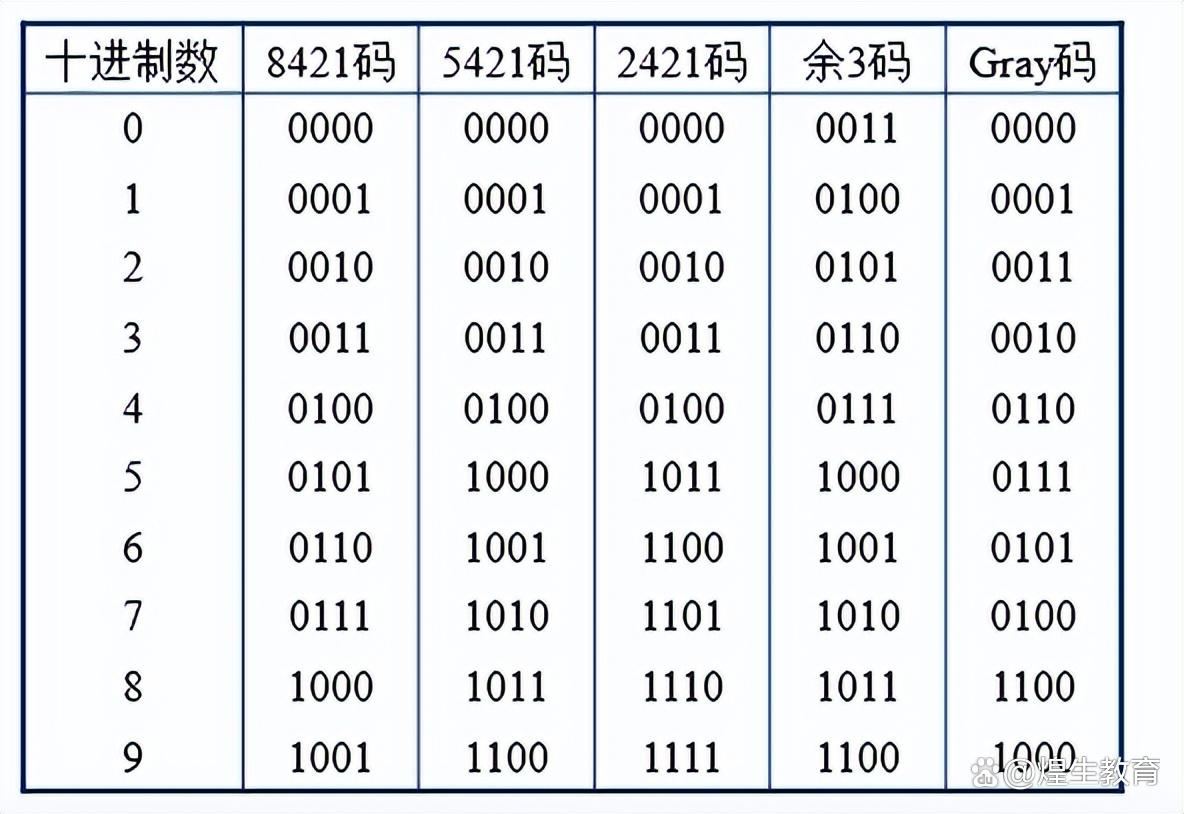

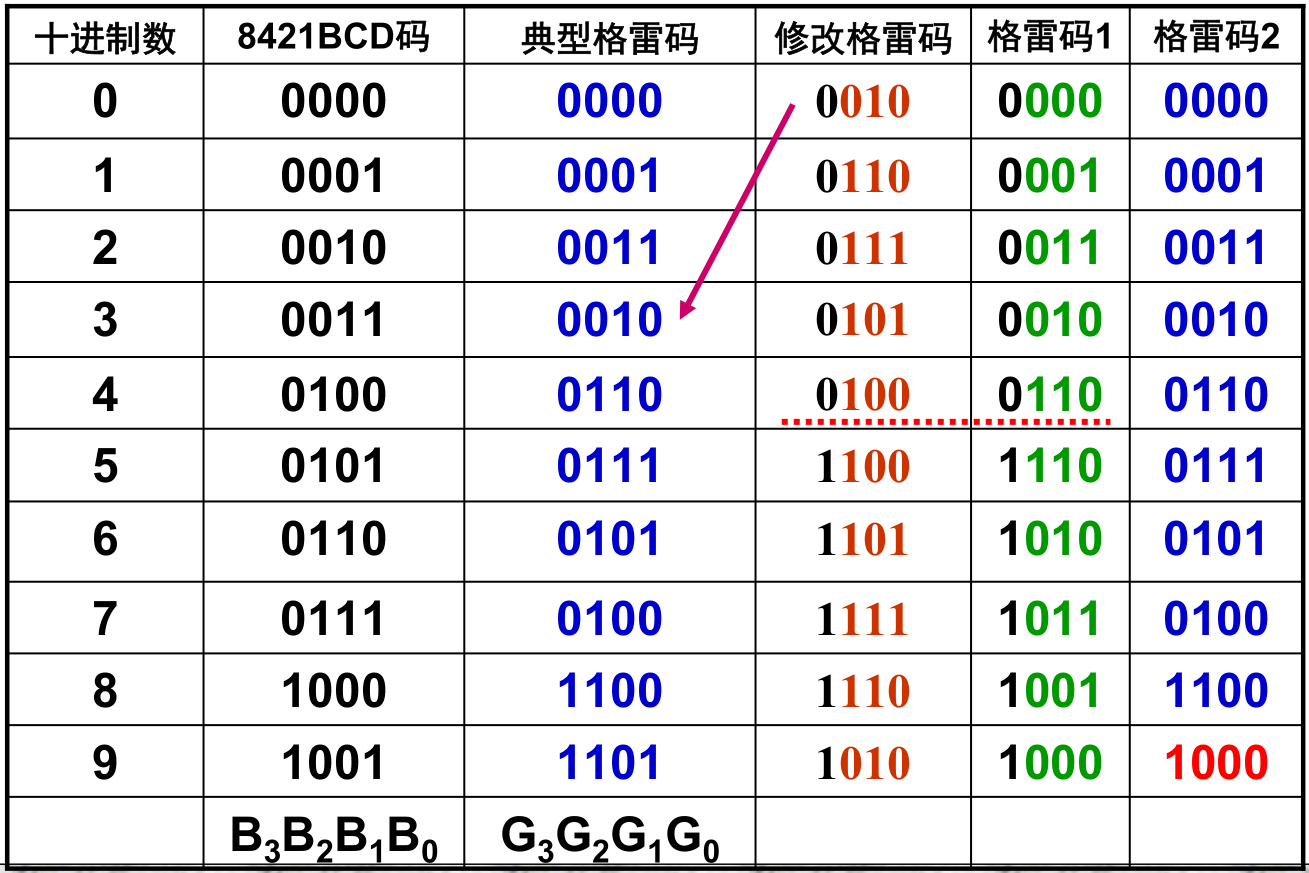

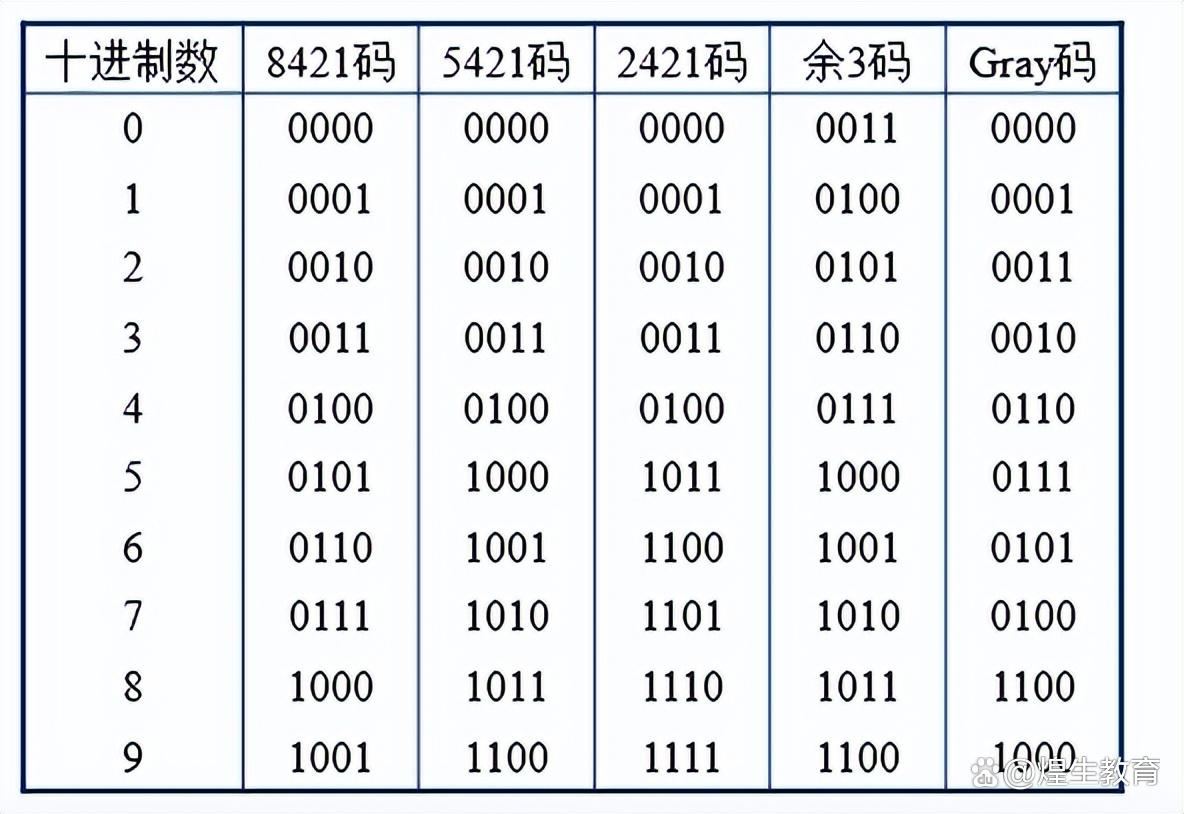

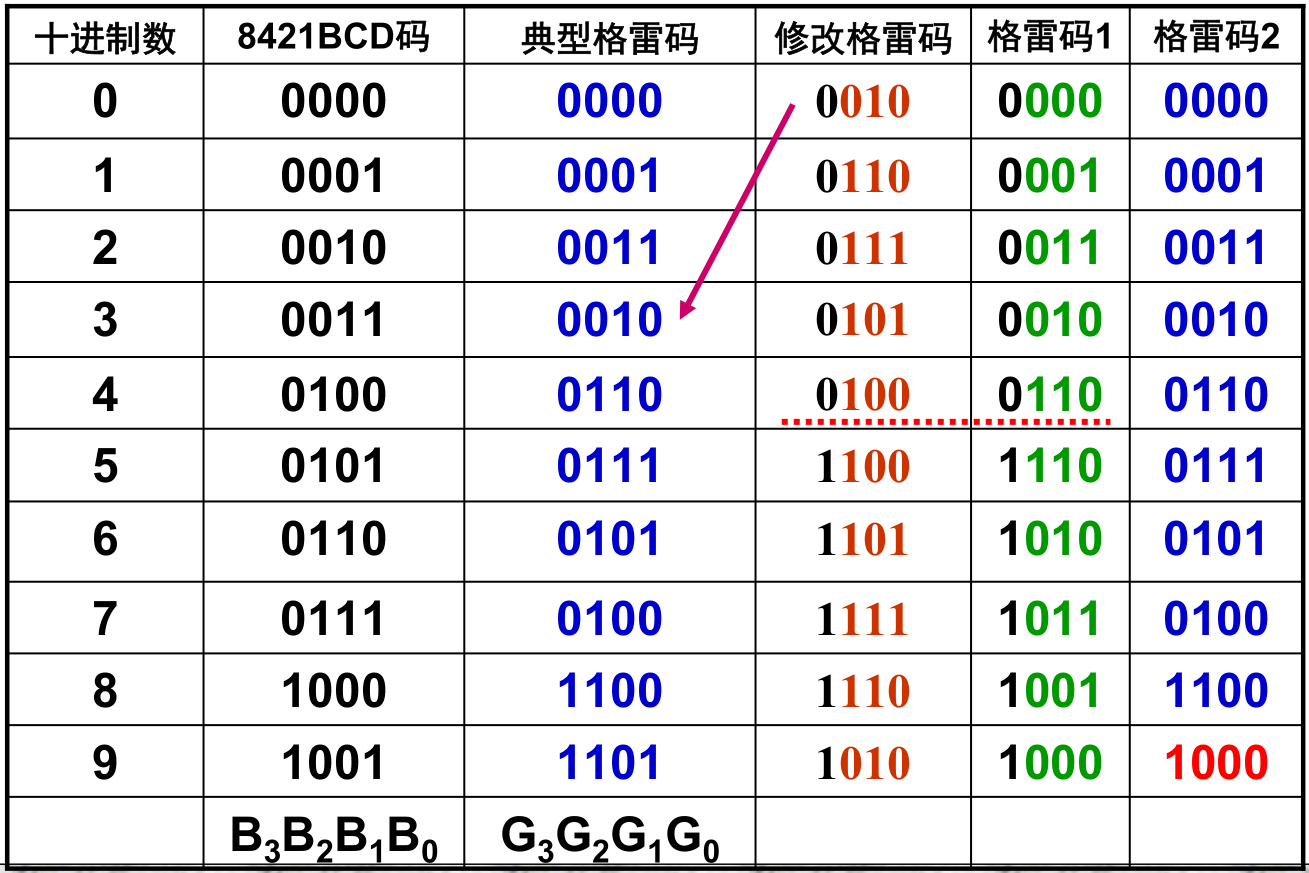

余3码的码表是什么,有什么特点呢?中文名称 余3码 定义 一种BCD码 形成 由8421码加3后形成的 特性 不具有有权性,但具有自补性 8421bcd码mooc雨课堂8421bcd码转余3码余3循环码最小项表达式同或运算余三循环码n个触发器可以构成最大计数长度为三态门真值表 概述 因为8421码中无1010~1111这6个代码,所以余3码中无0000~0010、1101...

设计一个四舍五入判别电路,其输入为8421BCD码,要求当输大于或等于5时...这题目太简单了。。首先画出真值表---大于5.。为1.小于,,在画出卡诺图,,,在写出逻辑表达式。。。最简式出来了。。再用逻辑门不就好了。。问题自己多想吧。。不然哪有进步。。。

双2-4译码器 74LS139真值表4、5、7上的非的意思是:输出低电平有效,即输出逻辑“0”。允许端为“L”时,4个输出端会有1个输出“L”,即“低电平”,或逻辑“0”。允许端为“H”时,4个输出端会全部输出“H”,即“高电平”,或逻辑“1”,视为无效。下图为真值表 ...

74LS192的引脚及具体功能以上为74ls192的引脚。以下为功能:P0、P1、P2、P3为计数器输入端,为清除端,Q0、Q1、Q2、Q3为数据输出端。74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,

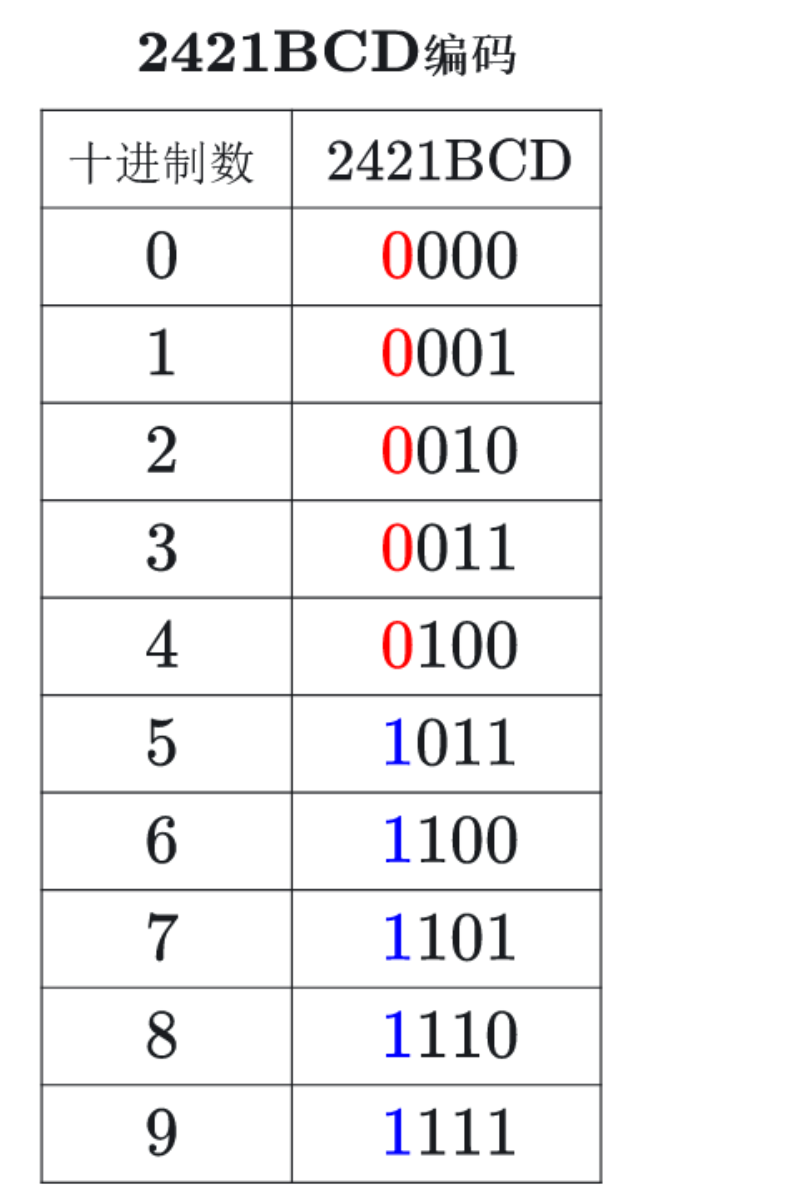

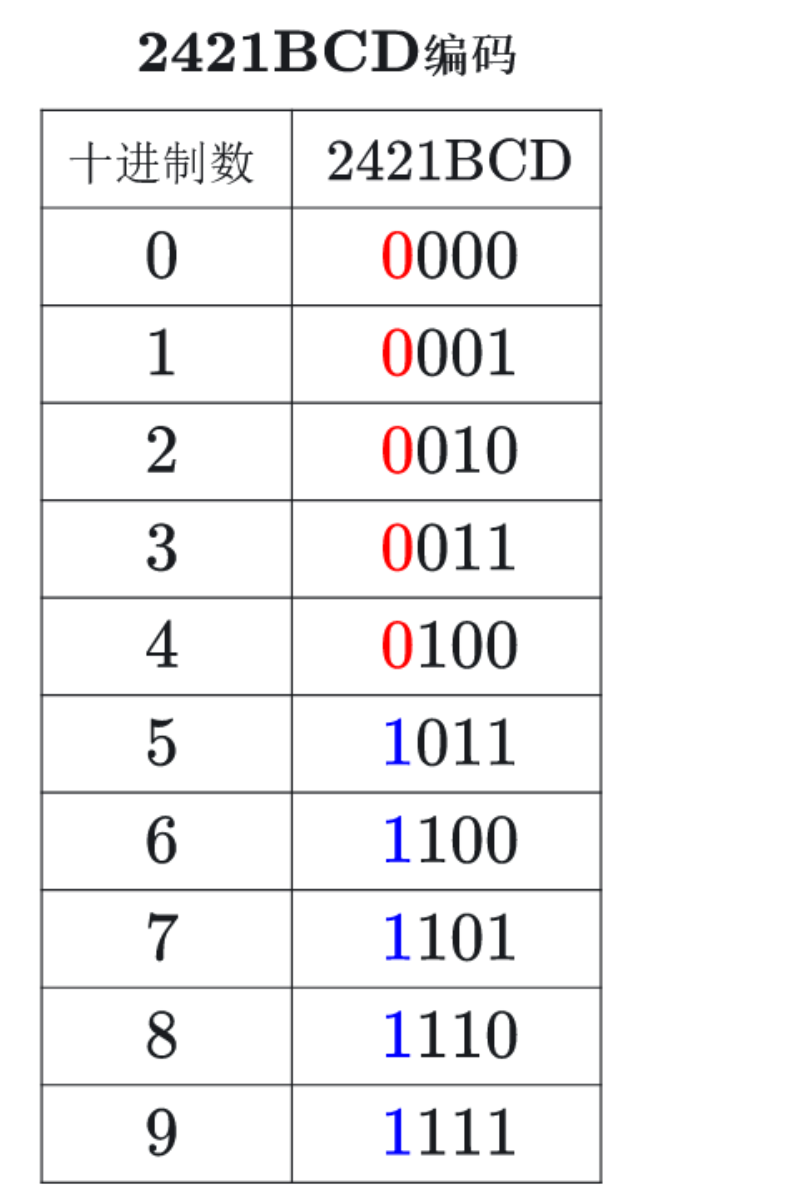

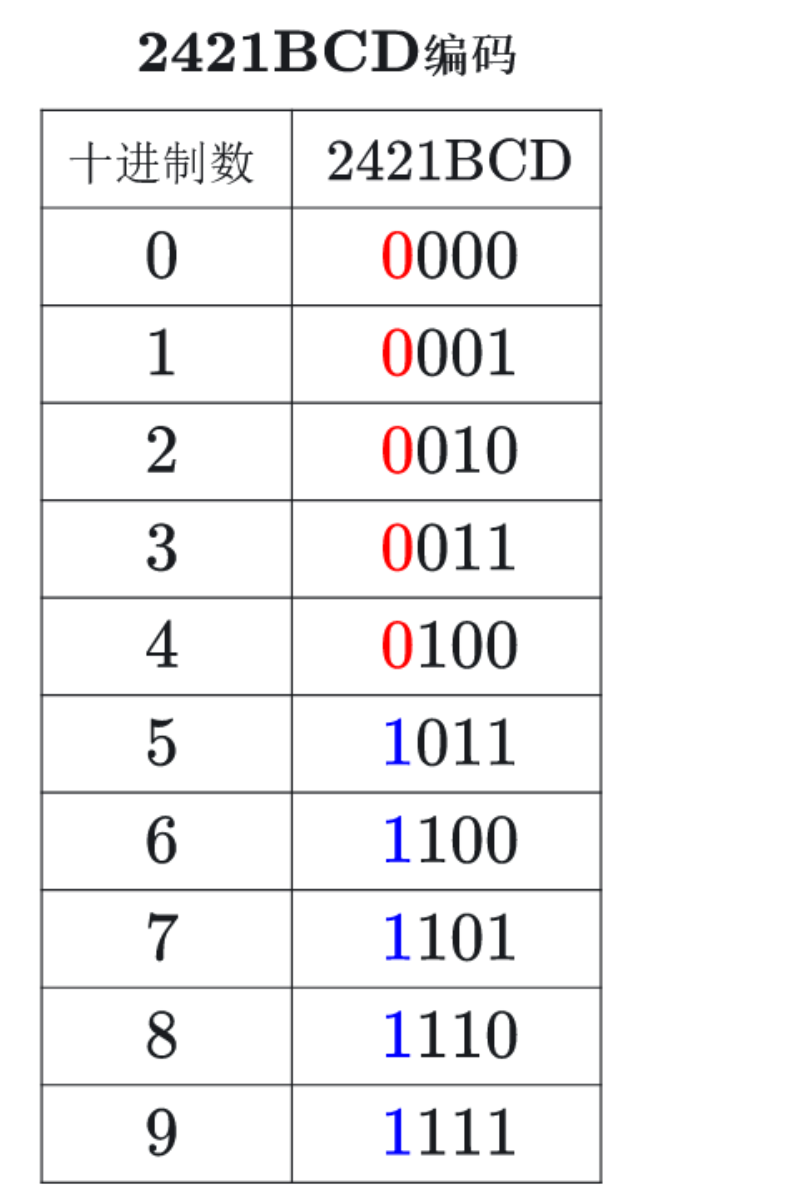

用与非门设计一个将2421码转换成8421码的转换电路列出真值表化简逻辑函数成与非式,然后再连接电路。multisim中自带真值表转逻辑函数的工具,这样也可以不用手工化简逻辑表达式。一位8421的BCD码只能表示0-9,0-9之间的素数只有2 3 5 7,8421BCD码每个数字只有一种表现形式,2 3 5 7分别表示为0010 0011 0101 0111,判断是否是这4个数字,判断方法...

自然二进制如何转换为8421BCD码因为他已经不是8421码了。比如十进制的6对应的8421码是0110,对应的二进制码也是0110。但是你想表示十进制的12,8421就是00010010,而自然二进制就是1100。二者的转化关系是:当二进制数大于1001(9)时,8421=自然二进制+0110(6),懂了没?真值表就不用我列了吧!参考资料:纯手打,望采纳!

余3码和2421两种BCD码转换为8421BCD码为了实现最少门电路芯片,设计了优化的真值表。具体连接方式如下图所示,展示了电路原理图和PCB图。电路原理图如下:图3 电路原理图 电路PCB图如下:图5 电路PCB图 总体来看,本设计成功实现余3码和2421BCD码到8421BCD码的译码电路,通过合理布局和元件选择,确保了准确可靠的码转换功能,同时优化电路...

集成电路74LS147有什么功能下面我们以TTL中规模集成电路74LS147为例介绍8421→BCD码优先编码器的功能。10线-4线8421BCD码优先编码器74LS147的真值表见表5。74LS147的引脚图如图5所示,其中第9脚NC为空。ls147的名称是优先编码器。根据查询相关公开信息,优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的输入...