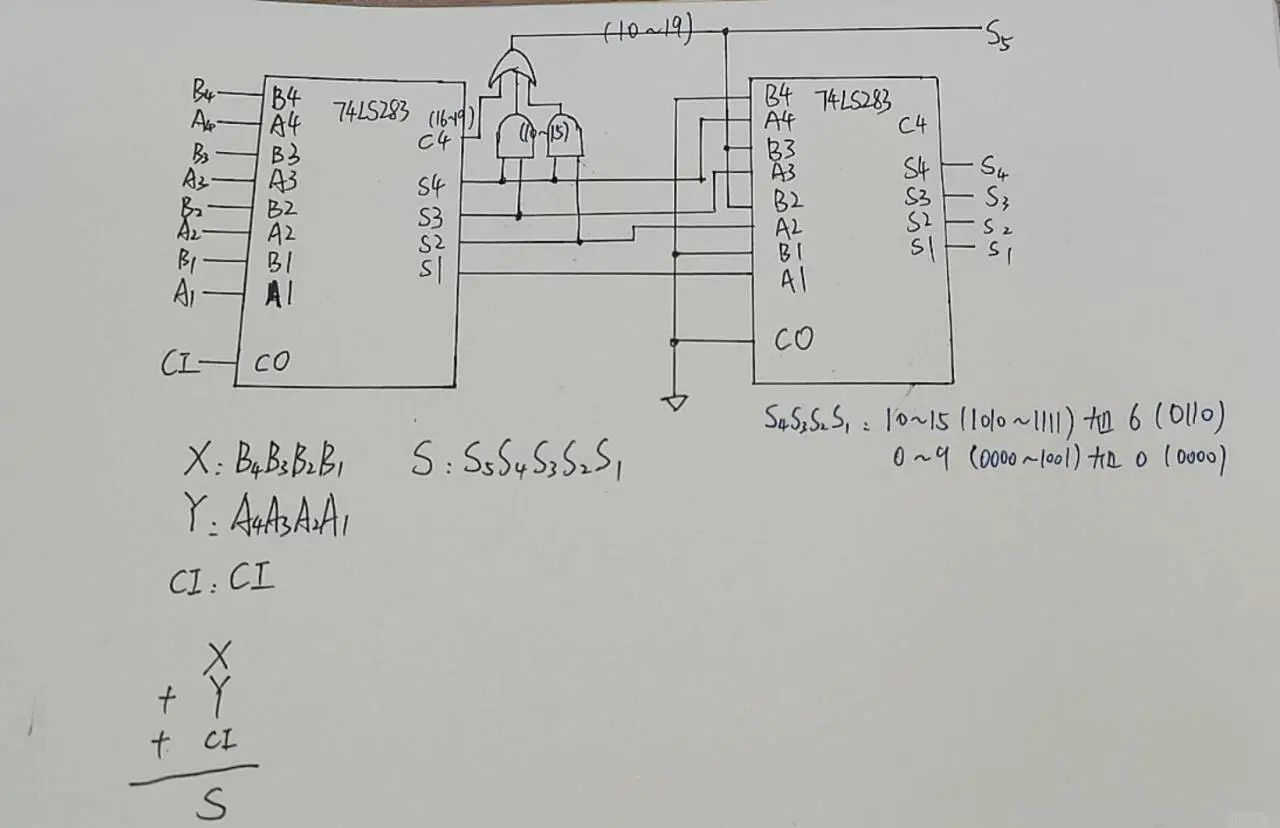

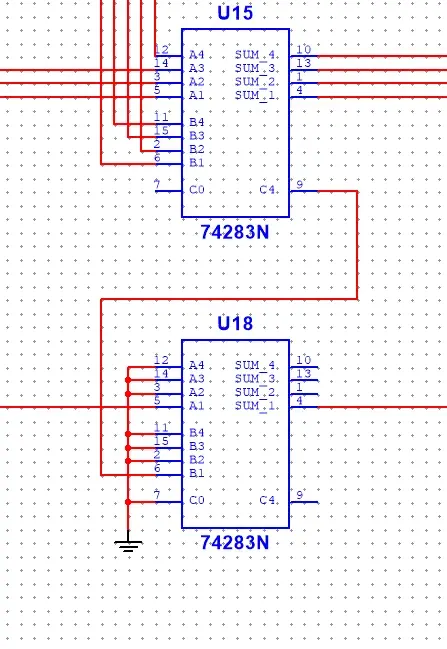

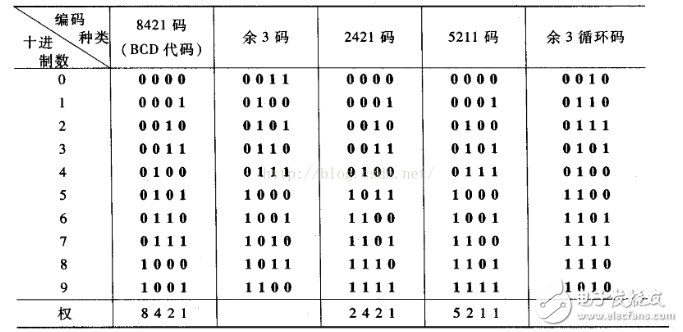

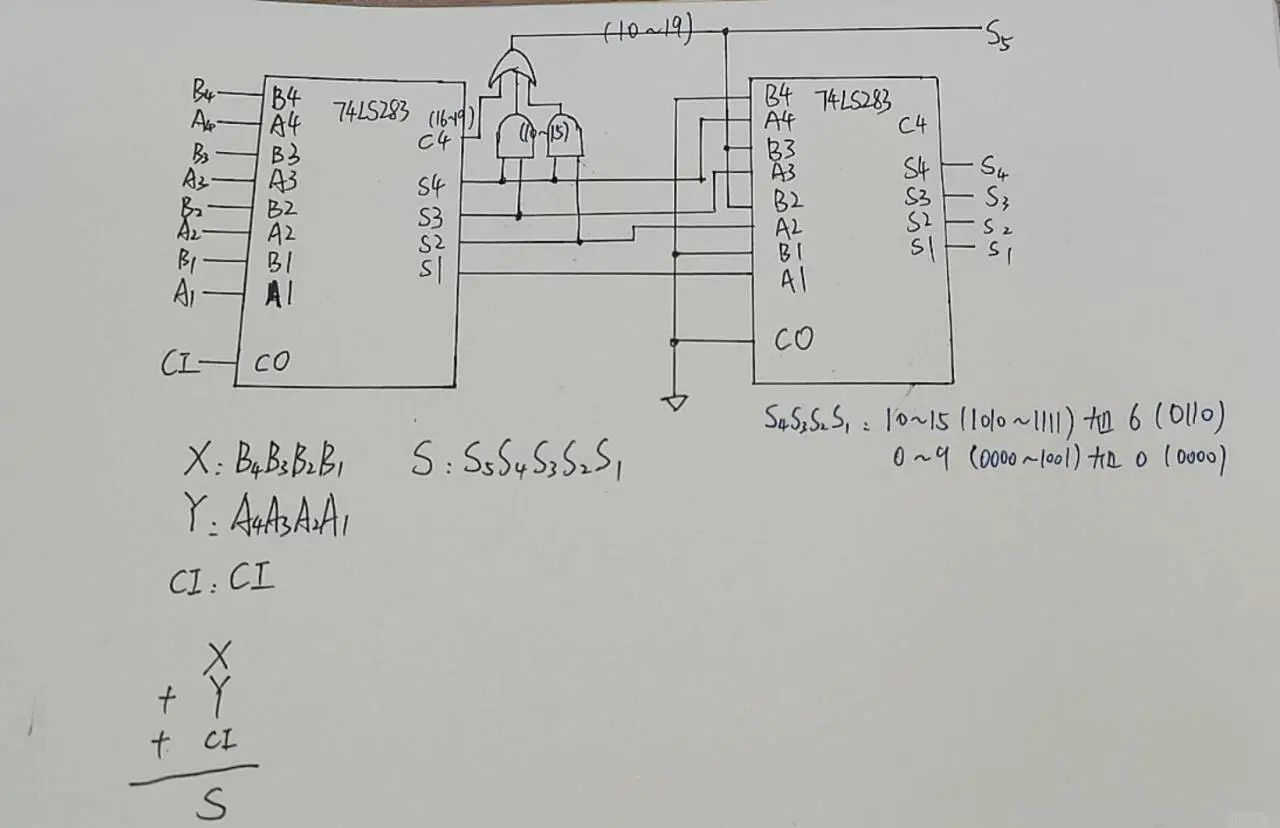

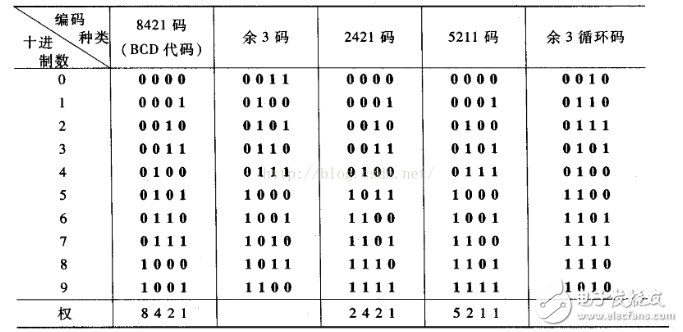

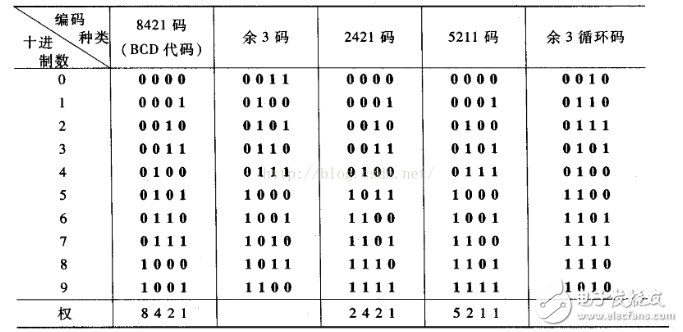

利用加法器设计一个代码转换电路,将bcd代码的8421码转换成余3码根据余3码的定义,这种编码方式是由8421码加上3形成的代码。因此,为了实现从8421码到余3码的转换,可以使用4位二进制并行加法器。在这个过程中,需要将8421码的四位二进制数A4、A3、A2和A1输入到并行加法器的输入端,同时将二进制数0011输入到B4、B3、B2和B1端,进位输入端C0则需要接上“0”。这

VHDL设计一个模为23的8421BCD码加法计算器在VHDL中设计一个模为23的8421BCD码加法计算器,需要实现一个名为bcd_cnt_1r0的实体。该实体包含一个时钟输入(clk)、一个复位信号(rst)、一个计数使能信号(cnt_en)和一个BCD输出(bcd_out)。计数器的模为23,因此其BCD输出的最大值为23。首先,定义常量和函数。常量ONES用于生成全1的信号。

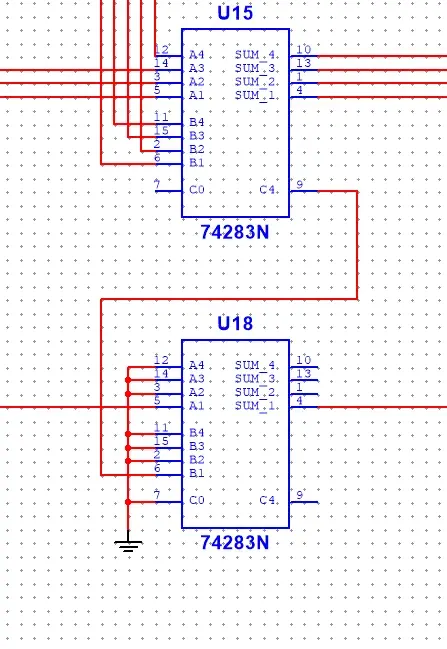

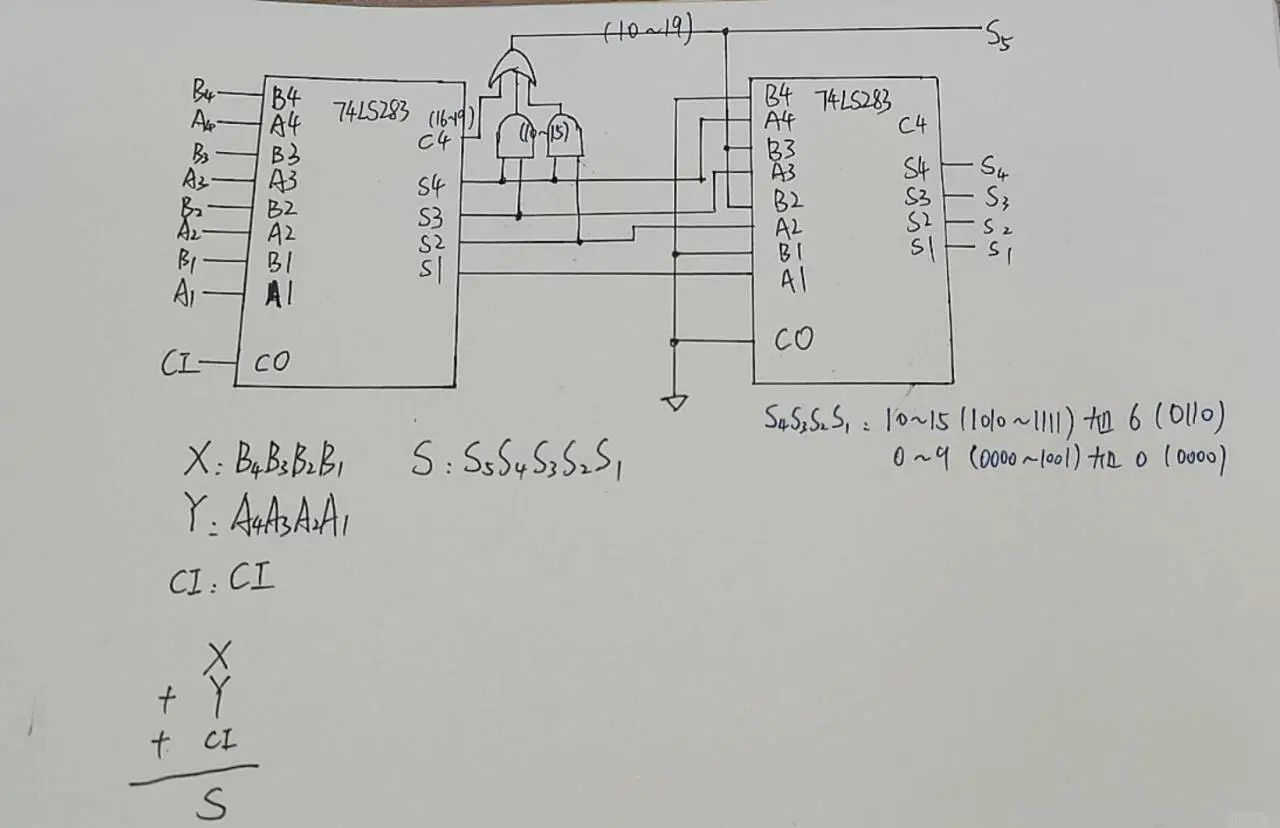

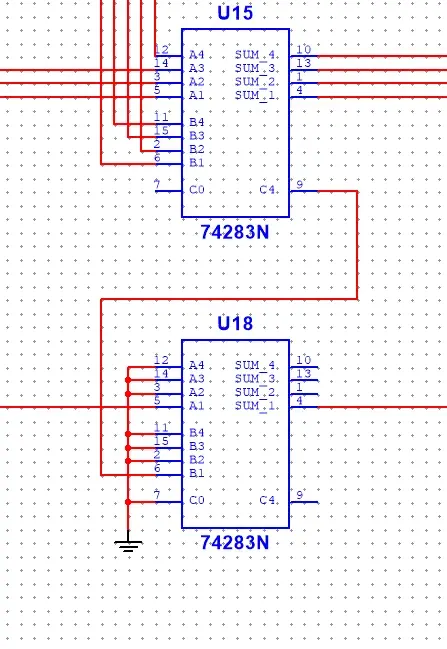

余三码8421bcd码转换电路设计的接线方法接线图:用4位二进制并行加法器实现8421码到余3码的转换,只需从4位二进制并行加法器的输入端A4、A3、A2和A1输入8421码,而从输入端B4、B3、B2和B1输入二进制数0011,进位输入端C0接上“0”。其次,在将两个余三码表示的十进制数相加时,能正确产生进位信号,但对“和”必须修正。修正的方法是...

使用一个4位二进制全加器,设计将8421码转换成余三码的电路,画出设计的...根据余3码的定义可知,余3码是由8421码加3后形成的代码。所以用4位二进制并行加法器实现8421码到余3码的转换,只需从4位二进制并行加法器的输入端A4、A3、A2和A1输入8421码;从输入端B4、B3、B2和B1输入二进制数0011,进位输入端C0接上“0”,便可从输出端F4、F3、F2和F1得到与输入8421码对应...

用74LS283设计一个码制转换器,将余3码转换成8421BCD码.列出其真值表...设计一个码制转换器,目标是将余3码转化为8421BCD码,需要理解余3码的性质。余3码实际上是8421码加3后的结果,通过并行加法器来实现这一转换。使用4位二进制并行加法器是关键。首先,将8421码的A4、A3、A2和A1输入到加法器的输入端A,对应位为0011的二进制数(即11)输入到B端,进位端C0保持为0...

设计一个逻辑电路,将一个8421BCD码转换为余三码,求电路图(010101111000)8421bcd=(010101111000)8421bcd=(100010101011)余3码=(100010101011)余3码 用

二进制怎么换成8421BCD码1)二进制 = (13.5)十进制=(0001 0011.0101)8421BCD码给个例子啊::二进制:1001010=74D8421BCD就是将7、4分别用4位的二进制表示出来:(01110100)8421BCD可以先换成十进制,再转换成8421码例如(1101.1)二进制 = (13.5)十进制=(0001 0011.0101)8421BCD码二进制怎么换成 8421BCD 码?

和8421bcd码(1010100)等值的二进制数是多少?8421BCD码是一种特殊的二进制编码方式,它可以将十进制数转换成二进制形式。这种编码方式的特点是每一位二进制数都代表十进制数中的一个数字,其中每一位的权重分别是8、4、2、1。因此,01010100对应的十进制数是54。如果你使用Windows的计算器进行转换,你会发现01010100对应的二进制数为110110。在使用...

...7485四位比较器实现两个1位8421BCD十进制数的加法电路A>B时,I(A>B)=1,加法器283的A数和B数分别是输入A的原码和B的反码,低位进位输入为1,故283的输出为A3A2A1A0+B3'B2'B1'B0'+1,其后两项是B的补码,即结果是S=A-B的补码运算。芯片是数据选择器,G1 G0A的输入值选择D7-D0传输至Y 。如:G1=G0=A=0 ,Y=D0=0 ,Y'=1 。G1...

二进制怎么换成8421BCD码首先,加3移位法以二进制数0000_101Xn(10+Xn)D为例。输入三位后,如果结果大于4,例如0101B等于5D,我们会加上3,即0101B+0011B=1000B,转换为BCD码就是0001_000Xn,对应十进制1Xn。设计思路包括四个模块:计数器、移位器、加法器和寄存器输出,通过状态机控制它们实现转换。通过仿真,17个时钟...